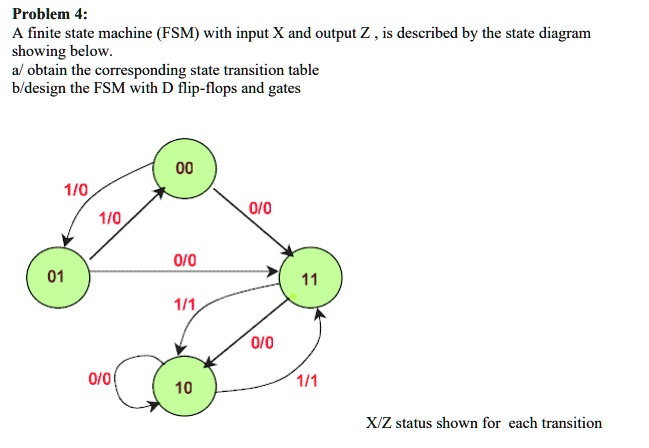

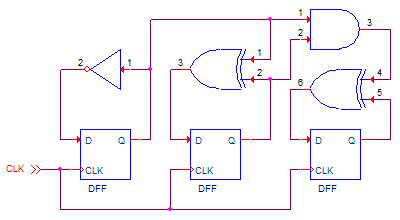

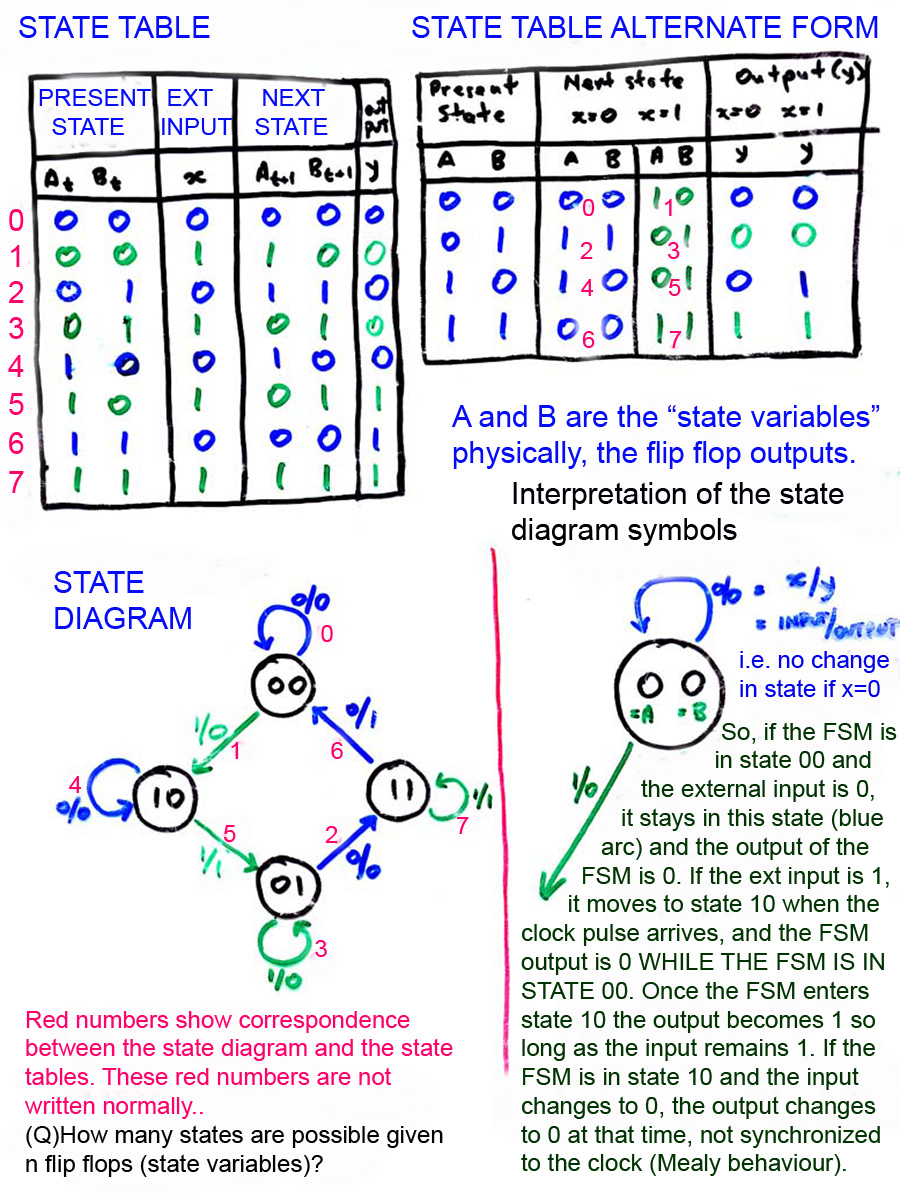

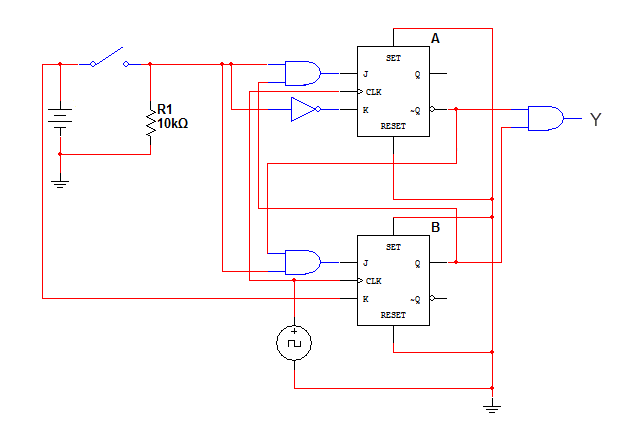

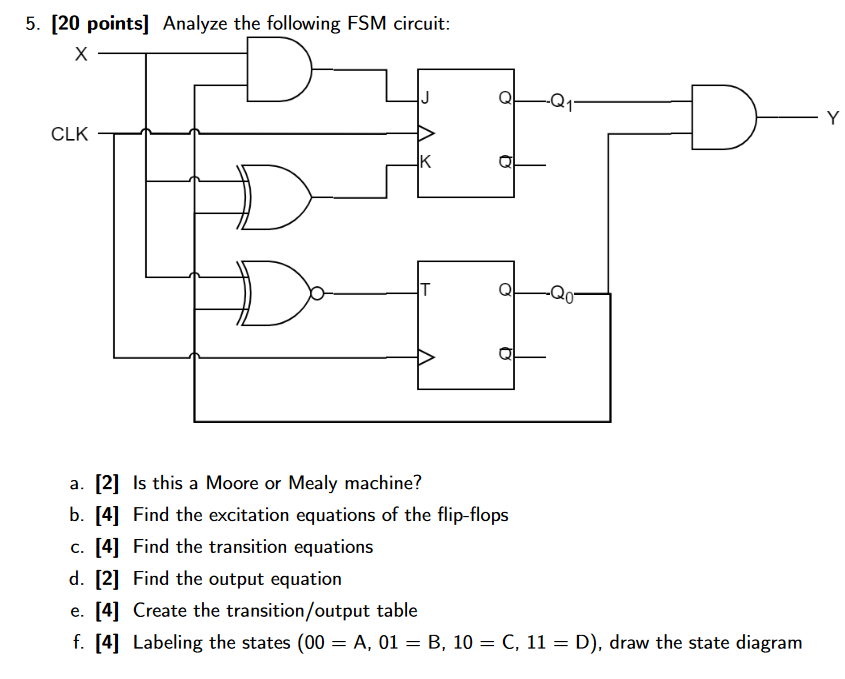

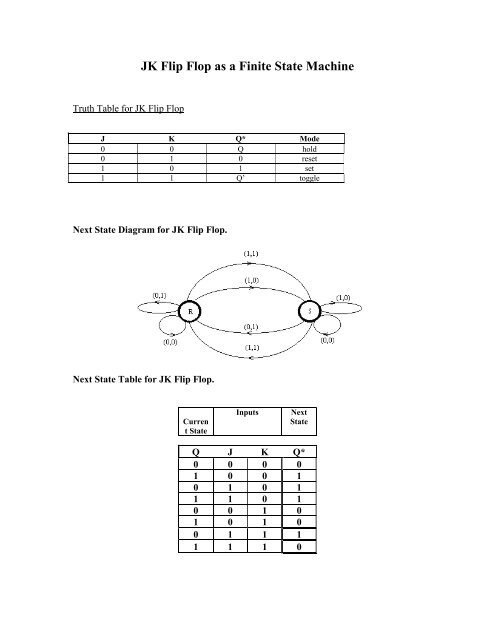

A finite state machine (FSM) is implemented using the D flip-flops A and B, and logic gates, as shown in the figure below. The four possible states of the FSM are QAQB =

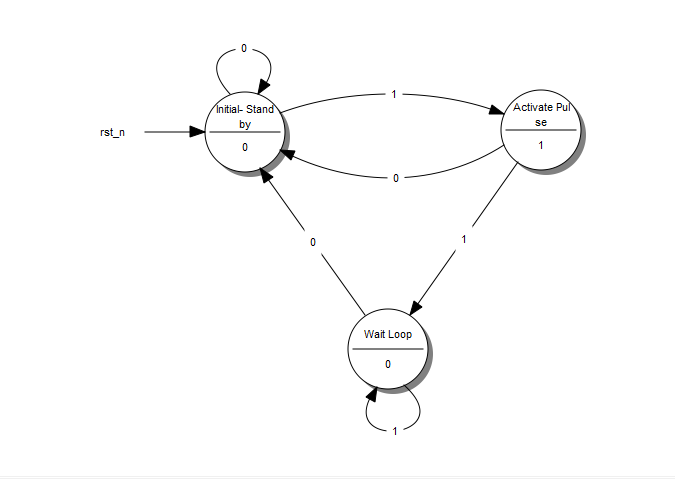

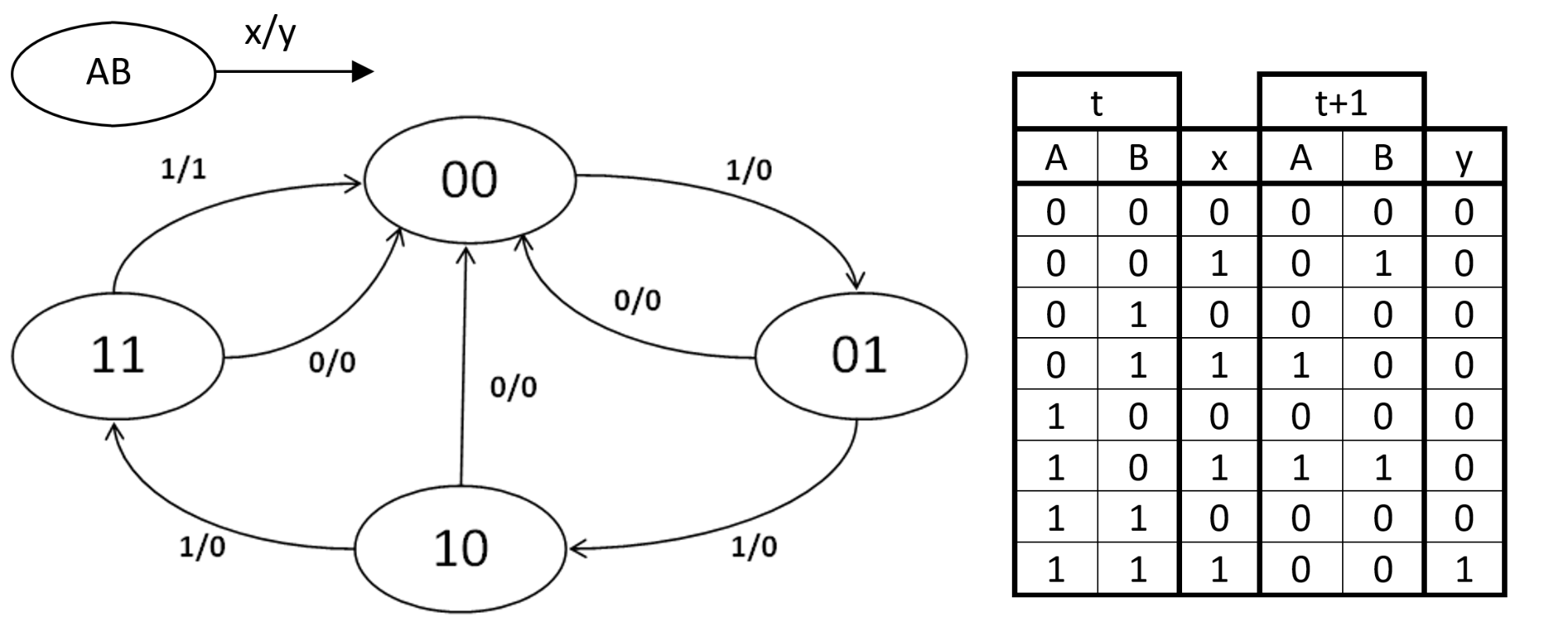

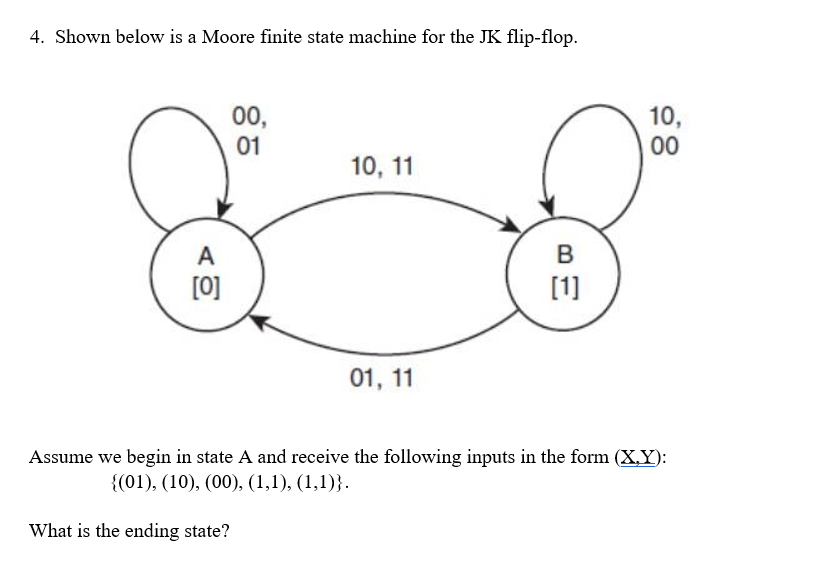

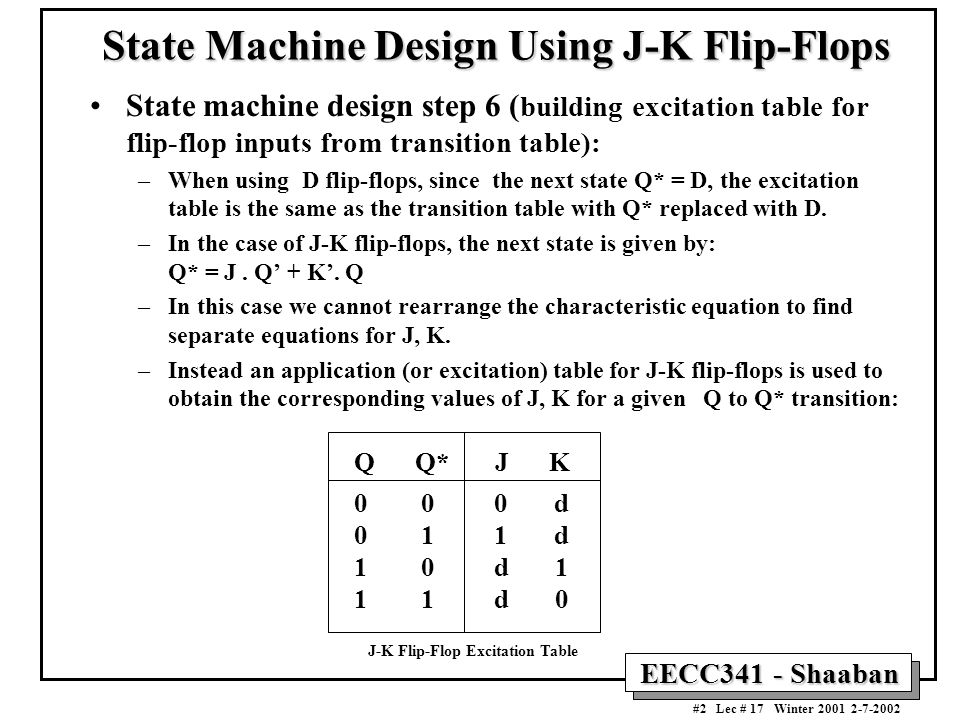

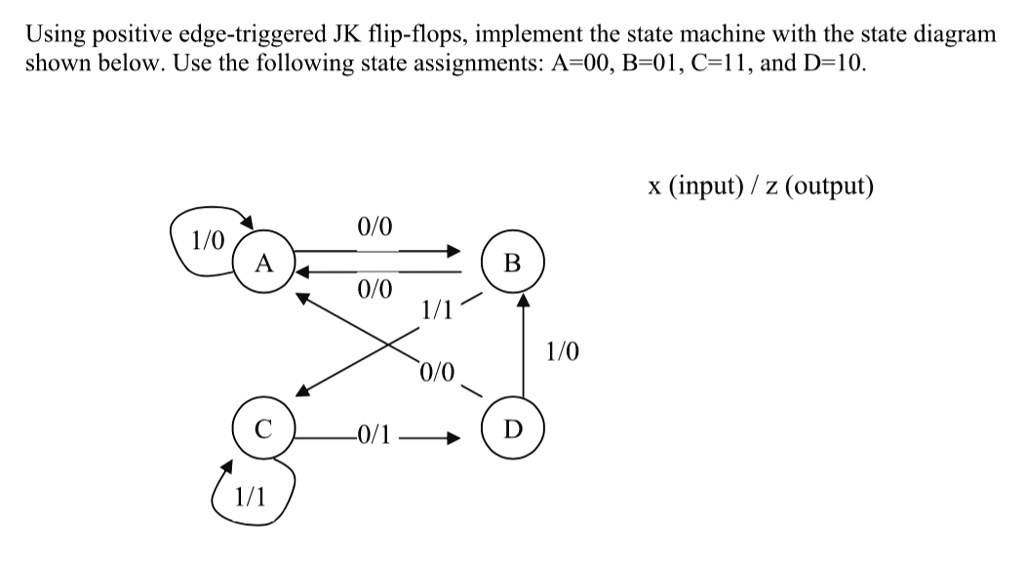

SOLVED: Implementing a State Machine Using JK Flip Flops Using positive edge-triggered JK flip-flops, we can implement a state machine with the state diagram shown below. The state assignments are as follows:

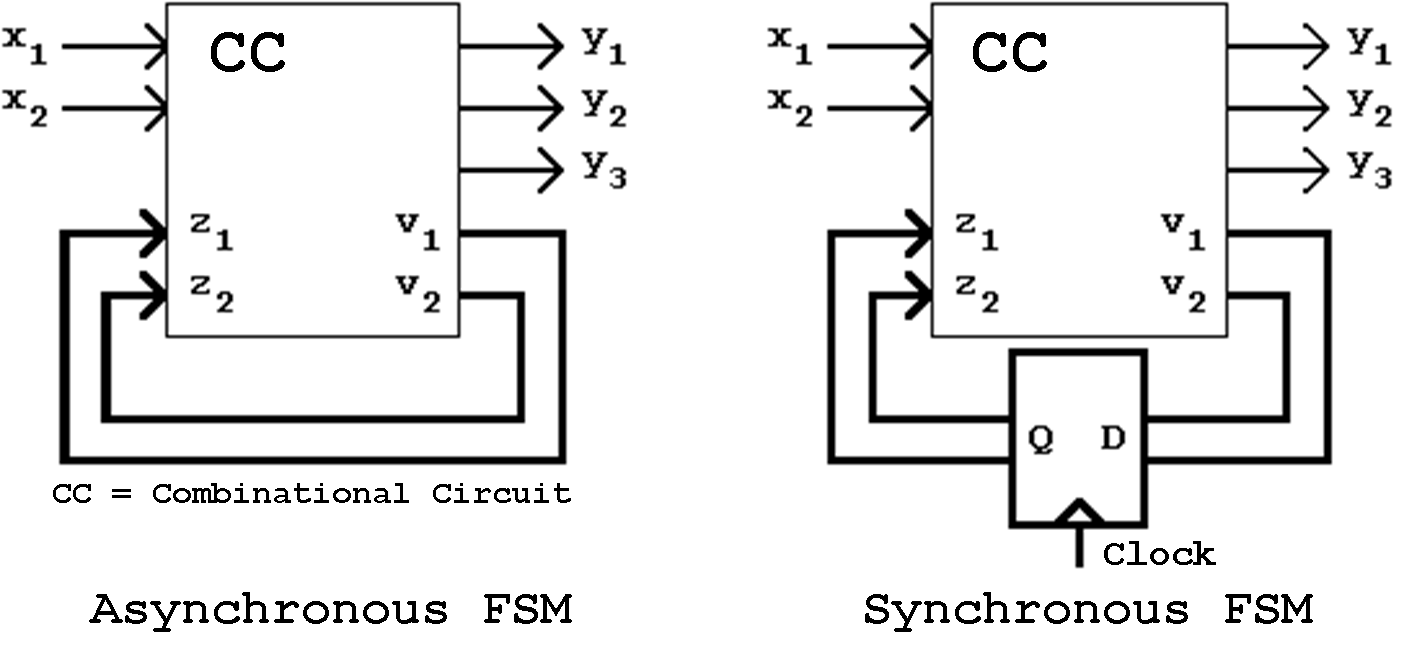

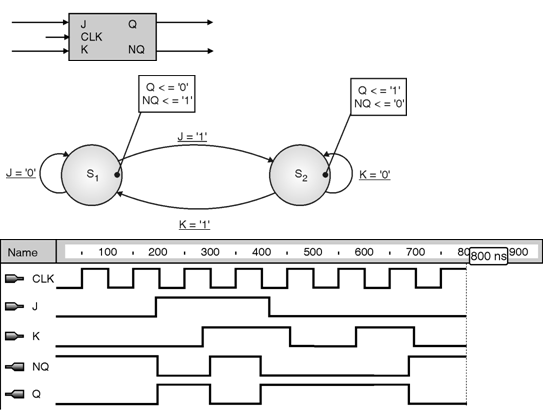

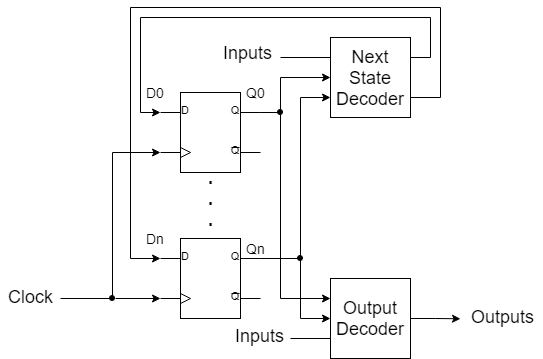

Moore design, clocked synchronous state machine utilizing positive-edge... | Download Scientific Diagram